# Part 3

# **Hardware Specifications**

# Introduction to the Hardware Specifications

The purpose of this section of the *Technical Reference Manual* is to provide enough information for a developer to test a system configuration using the HP-94 and accessories in typical usage. There are four major topics:

- Electrical Specifications

This provides voltage and current levels and specific integrated circuit (IC) information for some of the system ICs.

- Mechanical Specifications

This includes HP-94 dimensions and information about connector types and pin assignments.

- Environmental Specifications

This provides temperature, humidity, and other environmental information about the HP-94 operating environment.

- Accessory Specifications

This discusses the principal accessories currently available for the HP-94.

In addition, for reference by developers, data sheets are provided for four of the ICs used in the machine.

### Disclaimer

Hewlett-Packard makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

The information contained in this document is subject to change without notice.

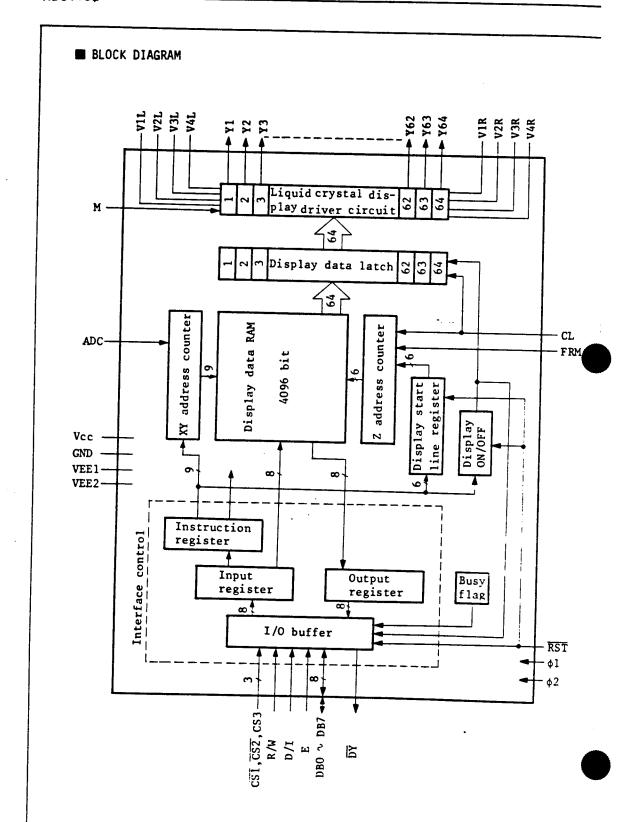

# **System Block Diagram**

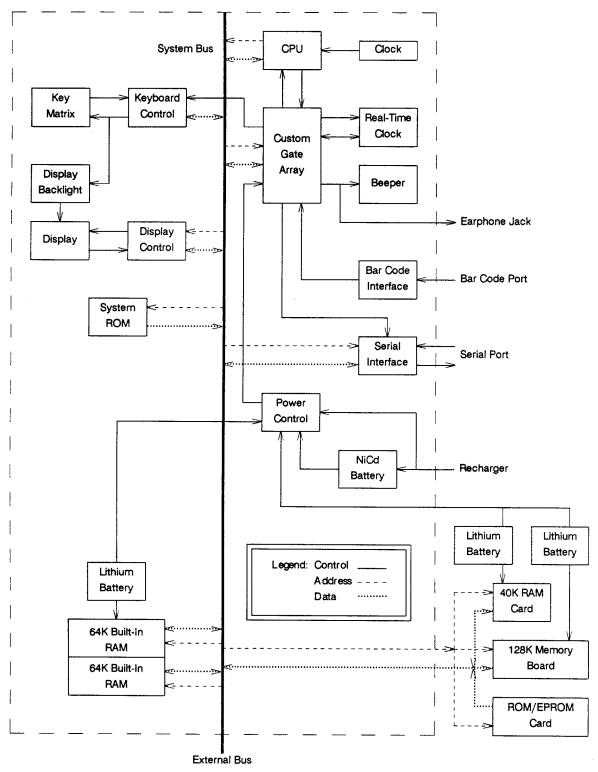

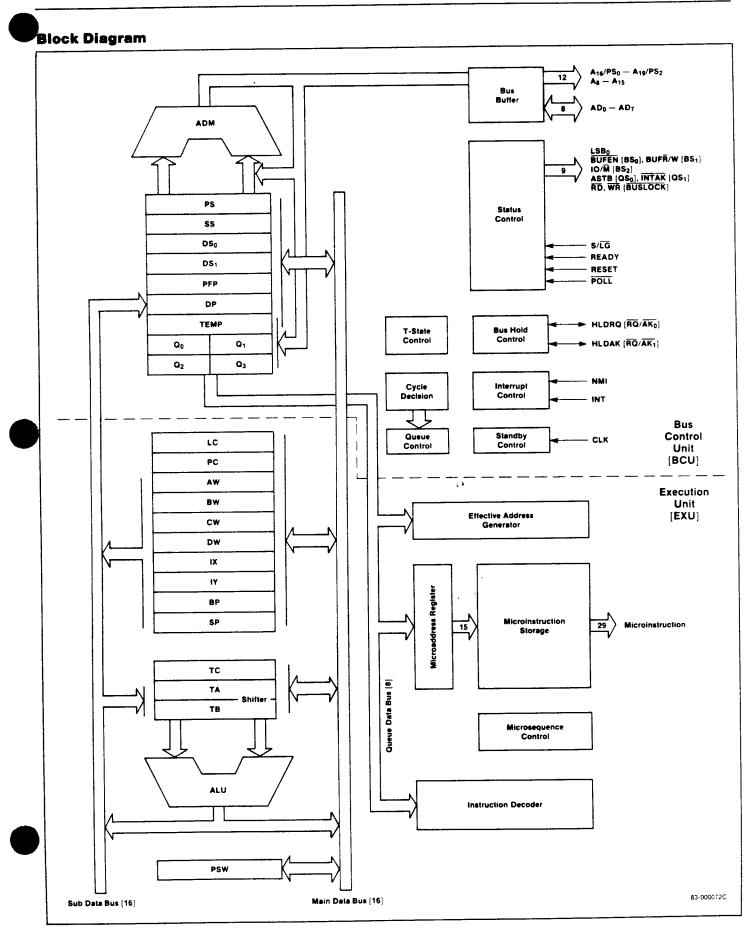

On the next page is a block diagram of the HP-94 hardware.

Figure 1. HP-94 Hardware Block Diagram

2 Introduction to the Hardware Specifications

# **Electrical Specifications**

# **Electrical Specifications**

This section provides the basic electrical specifications for the HP-94. Specific bus timing information is not provided. This information is available in the manufacturer's specifications for the individual components. The principal ICs used in the HP-94 are shown below.

Table 1-1. Principal Integrated Circuits

| IC                             | Manufacturer      | Part Number    |

|--------------------------------|-------------------|----------------|

| Microprocessor *               | NEC               | μPD70108 (V20) |

| RAM                            | Toshiba           | TC5565FL-15L   |

| EPROM                          | Toshiba           | TC57256D-20    |

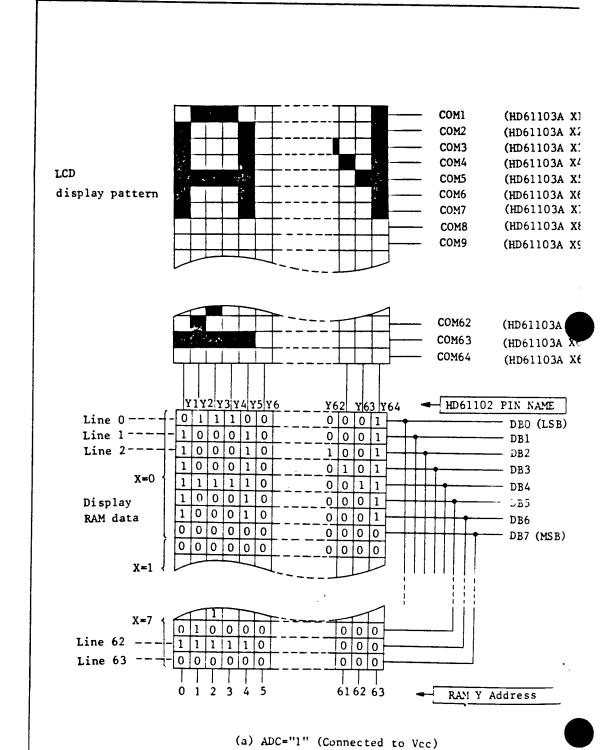

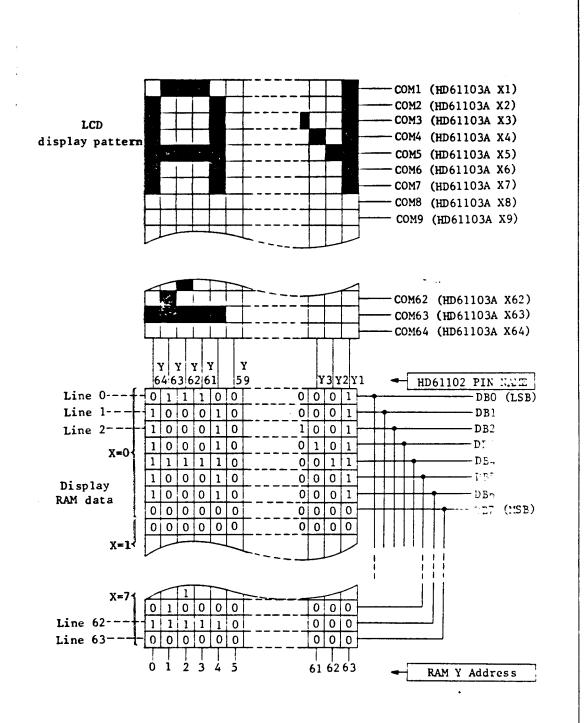

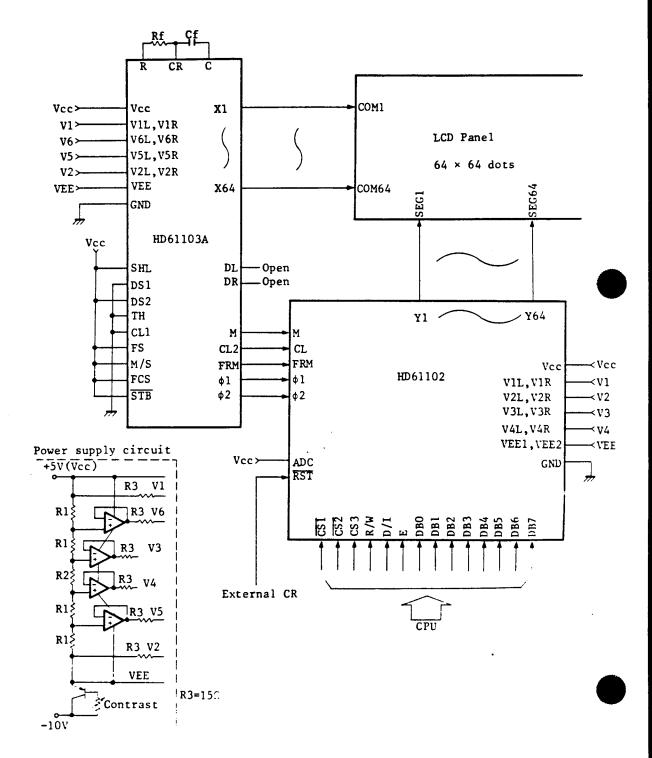

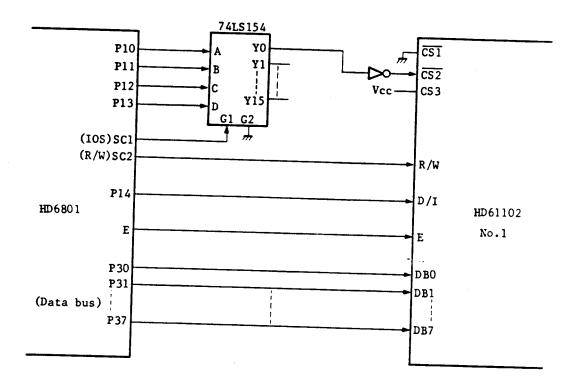

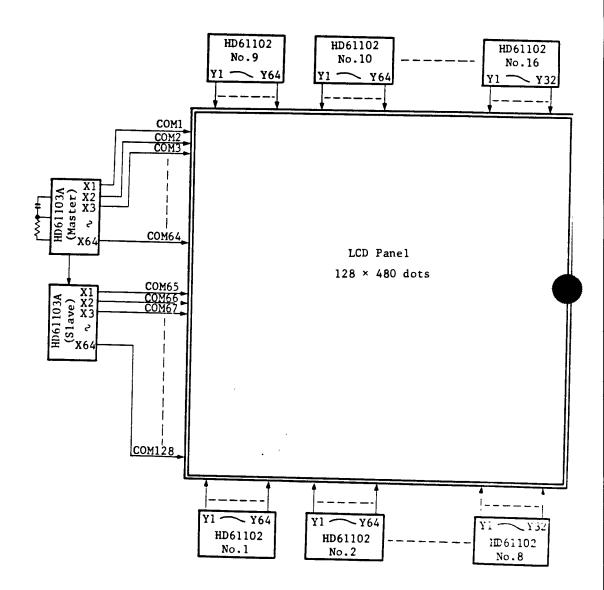

| LCD Column Driver *            | Hitachi           | HD61102A       |

| LCD Row Driver                 | Hitachi           | HD61103A       |

| UART *                         | ОКІ               | MSM82C51A      |

| Real-Time Clock *              | Epson             | RTC-58321      |

| Custom Gate Array              | Hitachi           | 61L224         |

| * Refer to the data sheets for | or these devices. |                |

Specific questions relating to the use of these ICs or their specifications should be directed to the IC manufacturer.

Table 1-2. Electrical Specifications

| 3               | 4.80<br>60<br>35<br>.6864<br>20<br>30               | 6.00<br>90<br>50                                                   | Vdc<br>mA<br>mA<br>MHz<br>mA                                                                                                                        | Varies as batteries vary Running Waiting for a key  * When backlight on  For HP-94F (256K RAM): T = 25 °C |

|-----------------|-----------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

|                 | 35<br>.6864<br>20<br>30<br>900                      | 50                                                                 | mA<br>MHz<br>mA<br>μA                                                                                                                               | Waiting for a key  * When backlight on  For HP-94F (256K                                                  |

|                 | 30<br>900                                           |                                                                    | MHz<br>mA<br>μA                                                                                                                                     | * When backlight on For HP-94F (256K                                                                      |

|                 | 20<br>30<br>900                                     | 100                                                                | mA<br>μA                                                                                                                                            | For HP-94F (256K                                                                                          |

|                 | 30<br>900                                           | 100                                                                | μΑ                                                                                                                                                  | For HP-94F (256K                                                                                          |

|                 | 900                                                 | 100                                                                |                                                                                                                                                     |                                                                                                           |

|                 |                                                     |                                                                    | mΛh                                                                                                                                                 |                                                                                                           |

| 55              |                                                     |                                                                    | man                                                                                                                                                 | HP 82430A Recharge-<br>able NiCd Battery Pack                                                             |

|                 | 4.60                                                | 4.65                                                               | Vdc                                                                                                                                                 | Discharging (voltage decreasing)                                                                          |

| 70              | 4.75                                                | 4.80                                                               | Vdc                                                                                                                                                 | Charging (voltage increasing)                                                                             |

| 35              | 2.70                                                | 2.75                                                               | Vdc                                                                                                                                                 |                                                                                                           |

| 35              | 4.40                                                | 4.45                                                               | Vdc                                                                                                                                                 |                                                                                                           |

| 30              |                                                     | 4.20                                                               | Vdc                                                                                                                                                 |                                                                                                           |

| 50              |                                                     |                                                                    | mA                                                                                                                                                  | For $V_{rs} = V_{cc}$ -0.1 V                                                                              |

| 5               |                                                     | + 15                                                               | Vdc                                                                                                                                                 | t                                                                                                         |

| V <sub>cc</sub> |                                                     |                                                                    | Vdc                                                                                                                                                 | †                                                                                                         |

|                 |                                                     | 0.15 V <sub>cc</sub>                                               | Vdc                                                                                                                                                 |                                                                                                           |

|                 |                                                     | V <sub>cc</sub>                                                    |                                                                                                                                                     | ‡                                                                                                         |

| )               |                                                     |                                                                    |                                                                                                                                                     |                                                                                                           |

|                 |                                                     | ±10<br>±3.5                                                        | μA<br>mA                                                                                                                                            | $V_{in} = V_{cc}$ or GND<br>$V_{in} = \pm 15 \text{ V}$                                                   |

|                 | 25                                                  |                                                                    | mA                                                                                                                                                  | When active with a std. RS-232-C load at 9600 baud and $V_{cc}$ =6.0 V                                    |

| '5              |                                                     |                                                                    | mA                                                                                                                                                  | For V <sub>bcr</sub> = V <sub>cc</sub> -0.1 V                                                             |

| V <sub>cc</sub> |                                                     | V <sub>cc</sub>                                                    | Vdc                                                                                                                                                 | CMOS 40H004                                                                                               |

| )               |                                                     |                                                                    |                                                                                                                                                     | inverting buffer                                                                                          |

|                 |                                                     | +1<br>-6                                                           |                                                                                                                                                     | Input logic 1 § Input logic 0 §                                                                           |

|                 | 65<br>35<br>30<br>60<br>5<br>V <sub>cc</sub><br>0.2 | 65 2.70<br>65 4.40<br>60<br>5<br>V <sub>cc</sub><br>0.2<br>0<br>25 | 0.15 V <sub>cc</sub> 0.15 V <sub>cc</sub> 0.2 V <sub>cc</sub> 0.2 ± 10 ± 3.5 0.15 V <sub>cc</sub> 0.15 V <sub>cc</sub> 0.15 V <sub>cc</sub> 0.2 0.2 | 35                                                                                                        |

<sup>\*</sup> Voltage and timing specifications associated with the external bus and memory port are established by the CPU voltage and timing specifications. Please refer to the NEC μPD70108 data sheet.

$<sup>\</sup>dagger$  The HP-94 has a special input protection circuit using a 4.7 volt zener diode clamp that keeps the input voltage less than 4.7 volts and greater than -0.6 volts. Input signals between 0 and  $V_{cc}$  will not be modified.

$<sup>\</sup>ddagger$  The output drivers are CMOS 40H004 inverting buffers that drive only between GND and  $V_{cc}$  voltage levels.

$<sup>\</sup>$  The bar code port input (V\_Obcr) drives a 40H004 inverting buffer with a 1 k $\Omega$  pullup resistor.

# **Mechanical Specifications**

# **Contents**

# Chapter 2 Mechanical Specifications

- **2-1** Physical Specifications

- **2-1** Serial Port Connector Specifications

- **2-2** Bar Code Port Connector Specifications

- **2-3** Memory Port Connector Specifications

- 2-5 External Bus Connector Specifications

- **2-7** Earphone Connector Specifications

- 2-7 Battery Pack Connector Specifications

# **Mechanical Specifications**

This chapter describes mechanical specifications for the HP-94 and its connectors.

# **Physical Specifications**

Below are the physical specifications for the HP-94.

Table 2-1. Physical Specifications

| Parameter | Value     | Units | Comments   |

|-----------|-----------|-------|------------|

| Height    | 16.0      | cm    | 6.3 in     |

| Width     | 16.5      | cm    | 6.5 in     |

| Thickness | 3.7       | cm    | 1.4 in     |

| Weight    | 686-745 * | g     | 1.5-1.6 lb |

<sup>\*</sup> The weight varies depending on the memory configuration. Minimum is for the HP-94D, and maximum is for the HP-94E with an HP 82412A ROM/EPROM Card containing three 27C256 EPROMs.

# **Serial Port Connector Specifications**

The serial port connector is a 15-pin D-type female connector. The connector's attachment bolts use  $4-40 \times 1/4$ " slotted-head screws; note that it is not necessary to secure cables to the machine using these bolts. The following tables provide serial port connector pin assignments and information about mating connectors for the serial port.

Table 2-2. Serial Port Connector Pin Assignments

| Pin Number | Symbol             | Signal Name               |

|------------|--------------------|---------------------------|

| Housing    | FG                 | Frame Ground              |

| 1          | NC NC              | Not Connected             |

| 2          | TxD                | Transmitted Data          |

| 3          | RxD                | Received Data             |

| 4          | RTS                | Request To Send           |

| 5          | CTS                | Clear To Send             |

| 6          | DSR                | Data Set Ready            |

| 7          | SG                 | Signal Ground             |

| 8          | DCD                | Data Carrier Detect       |

| 9          | V <sub>rs</sub>    | Switched V <sub>cc</sub>  |

| 10         | V <sub>rch</sub> * | Alternate Recharger Input |

| 11         | GND                | Recharger Ground Return   |

| 12-14      | NC                 | Not Connected             |

| 15         | DTR                | Data Terminal Ready       |

<sup>\*</sup> The specifications for Vrch to allow charging of the NiCd battery pack using this pin are the same values as the output voltage and current specifications of the HP 82431A recharger.

**Table 2-3. Serial Port Mating Connectors**

| Manufacturer | Part Number |

|--------------|-------------|

| TRW          | DAM 15P     |

| Amphenol     | 17-20150-1  |

| JAE          | DAC 15P     |

| ITT Cannon   | DA-15P      |

# **Bar Code Port Connector Specifications**

The bar code port uses a 6-pin, 240° circular DIN connector. Either a 5-pin or 6-pin mating connector can be used on the bar code reader since pin 6 is not connected at the bar code port. The following tables provide bar code port connector pin assignments and information about mating connectors for the bar code port.

Table 2-4. Bar Code Port Connector Pin Assignments

| Pin Number | Symbol           | Signal Name               |

|------------|------------------|---------------------------|

| 1          | V <sub>bcr</sub> | Switched V <sub>cc</sub>  |

| 2          | $V_{Obcr}$       | Input From Barcode Reader |

| 3          | GND *            | Signal Ground             |

| 4-6        | NC               | Not Connected             |

Table 2-5. Bar Code Port Mating Connectors

| Manufacturer | Part Number |

|--------------|-------------|

| Switchcraft  | 12BL5M      |

| Switchcraft  | 12BL6M      |

| ITT Cannon   | 46005F      |

| ITT Cannon   | 46006       |

| TRW          | 014-00016-5 |

| TRW          | 014-00024-1 |

| SMK          | DIN45322    |

# **Memory Port Connector Specifications**

The memory port connector is inside the back cover of the HP-94, and is where the 40K RAM card, ROM/EPROM card, and 128K memory board connect to the machine. It is a Burndy PSE36C-2 36-pin PCB edge connector. The pin assignment is shown below.

Table 2-6. Memory Port Connector Pin Assignments

| Pin | Symbol           | Signal Name                     |

|-----|------------------|---------------------------------|

| 1   | GND              | Ground                          |

| 2   | RD               | Read                            |

| 3   | WR               | Write                           |

| 4   | CSV              | System reset                    |

| 5   | A0               | Address bit 0                   |

| 6   | A1               | Address bit 1                   |

| 7   | A2               | Address bit 2                   |

| 8   | A3               | Address bit 3                   |

| 9   | A4               | Address bit 4                   |

| 10  | <b>A</b> 5       | Address bit 5                   |

| 11  | A6               | Address bit 6                   |

| 12  | <b>A</b> 7       | Address bit 7                   |

| 13  | A8               | Address bit 8                   |

| 14  | A9               | Address bit 9                   |

| 15  | A10              | Address bit 10                  |

| 16  | A11              | Address bit 11                  |

| 17  | A12              | Address bit 12                  |

| 18  | A13              | Address bit 13                  |

| 19  | A14              | Address bit 14                  |

| 20  | A15_             | Address bit 15                  |

| 21  | CSMC1 *          | Memory card chip select 1       |

| 22  | CSMC2 †          | Memory card chip select 2       |

| 23  | AD0              | Address/data bit 0              |

| 24  | AD1              | Address/data bit 1              |

| 25  | AD2              | Address/data bit 2              |

| 26  | AD3              | Address/data bit 3              |

| 27  | AD4              | Address/data bit 4              |

| 28  | AD5              | Address/data bit 5              |

| 29  | AD6              | Address/data bit 6              |

| 30  | AD7              | Address/data bit 7              |

| 31  | CSV              | System reset                    |

| 32  | V <sub>ni</sub>  | NiCd battery voltage (output)   |

| 33  | V <sub>mcs</sub> | Lithium battery voltage (input) |

| 34  | V <sub>ad</sub>  | Recharger DC voltage (output)   |

| 35  | $V_{cc}$         | Supply voltage                  |

| 36  | GND              | Ground                          |

<sup>\*</sup> CSMC1 is active when A19, A18, and A16 = 0 and A17 = 1 (CSMC1 = A19-A18-A17-A16).

<sup>†</sup>  $\overline{\text{CSMC2}}$  is active when A19 and A18 = 0, and A17 and A16 = 1 ( $\overline{\text{CSMC2}}$  =  $\overline{\text{A19}}\cdot\overline{\text{A18}}\cdot\text{A17}\cdot\text{A16}$ ).

# **External Bus Connector Specifications**

The external bus connector is located on the underside of the HP-94 behind a hard plastic port cover. The connector is a JAE PICL-40S-ST. Connection to the external bus connector can be made using a JAE PICL-40P-ST connector. The pin assignment is shown in the following table. Pin 1 is marked on the connector body. The odd-numbered pins are on the outer row (toward the outer edge of the HP-94 case), and the even-numbered pins are on the inner row.

Table 2-7. External Bus Connector Pin Assignments

| Pin | Symbol            | Signal Name                  |

|-----|-------------------|------------------------------|

| 1   | V <sub>ni</sub>   | NiCd battery voltage         |

| 2   | V <sub>ni</sub>   | NiCd battery voltage         |

| 3   | V <sub>cc</sub>   | Supply voltage               |

| 4   | GND               | Ground                       |

| 5   | NC                | Not connected                |

| 6   | NC                | Not connected                |

| 7   | NC_               | Not connected                |

| 8   | DT/R              | Buffer read/write            |

| 9   | DEBUG             | Connected to ground          |

| 10  | NC                | No connection                |

| 11  | IRQFK             | Reserved interrupt request 2 |

| 12  | IRQPR             | Reserved interrupt request 1 |

| 13  | IO/M              | IO/Memory                    |

| 14  | ALE               | Address latch enable         |

| 15  | CLK               | CPU clock                    |

| 16  | AS16              | Address/status bit 16        |

| 17  | AS17              | Address/status bit 17        |

| 18  | AS18              | Address/status bit 18        |

| 19  | AS19              | Address/status bit 19        |

| 20  | RESET             | System clocked reset         |

| 21  | AD0               | Address/data bit 0           |

| 22  | AD1               | Address/data bit 1           |

| 23  | AD2               | Address/data bit 2           |

| 24  | AD3               | Address/data bit 3           |

| 25  | AD4               | Address/data bit 4           |

| 26  | AD5               | Address/data bit 5           |

| 27  | AD6               | Address/data bit 6           |

| 28  | AD7               | Address/data bit 7           |

| 29  | A15               | Address bit 15               |

| 30  | A14               | Address bit 14               |

| 31  | A13               | Address bit 13               |

| 32  | A12               | Address bit 12               |

| 33  | A11               | Address bit 11               |

| 34  | A10               | Address bit 10               |

| 35  | <b>A</b> 9        | Address bit 9                |

| 36  | <u> <b>A</b>8</u> | Address bit 8                |

| 37  | WR                | Write                        |

| 38  | RD                | Read                         |

| 39  | GND               | Ground                       |

| 40  | GND               | Ground                       |

# **Earphone Connector Specifications**

The earphone jack accepts a 3.5 mm miniature plug, with an overall length of less than 12 mm. A 0.125 inch diameter miniature plug will also fit, but will tend to have a lower insertion and removal force. Most standard earphones will connect properly to the HP-94 both mechanically and electrically. Some variation in audio output volume will occur between various earphone manufacturers.

# **Battery Pack Connector Specifications**

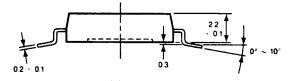

The battery pack uses two AMP 42827-1 brass contacts. The HP-94 mates these contacts with custom nickel-plated brass pins that are 2.31 mm (0.091 in) nominal diameter, 6.3 mm (0.25 in) long, and 6.0 mm (0.24 in) center spacing.

# **Environmental Specifications**

# **Environmental Specifications**

Below are the environmental specifications for the HP-94.

**Table 3-1. Environmental Specifications**

| Parameter             | Min                                                          | Max | Units Comments |               |  |

|-----------------------|--------------------------------------------------------------|-----|----------------|---------------|--|

| Operating Temperature | 0 55                                                         |     | °C             | +32 to 131 °F |  |

| Storage Temperature   | -40                                                          | 65  | °C             | -40 to 149 °F |  |

| Operating Humidity    | 0                                                            | 95  | %RH            | At 40 °C      |  |

| Vibration             | 3.4 g rms, 5 to 500 Hz random vibration, 10 minutes per axis |     |                |               |  |

|                       | Swept sine, 1 g, 5 to 500 Hz, 10 minutes dwell at resonance  |     |                |               |  |

| Shock                 | 3 ms, 1/2 sine wave, 228 g, 6 axes                           |     |                |               |  |

# **Accessory Specifications**

# **Contents**

### **Chapter 4 Accessory Specifications** 4-1 40K RAM Card Specifications **ROM/EPROM Card Specifications** 4-2 4-3 **Battery Pack Specifications** 4-4 Guidelines for Using Rechargeable Batteries 4-4 **Recharger Specifications** Level Converter Specifications 4-5 4-6 When to Use the Level Converter 4-7 Cables 4-7 Modem Cable 4-8 Printer Cable Level Converter Cable 4-8 4-9 Vectra Cable Vectra or IBM PC/AT to Level Converter Cable 4-9 IBM PC or PC/XT to Level Converter Cable 4-10 4-10 Bar Code Readers 4-10 Connecting the Serial Port to a Smart Wand

# **Accessory Specifications**

The principal HP-94 hardware accessories (at the time of printing) are listed below. This accessory list does not include any software documentation, development tools, or utilities. For a complete list of all HP-94 accessories and support items, please refer to the current HP-94 price list, available at all HP sales offices. This chapter will describe only accessories listed in the table below.

Table 4-1. HP-94 Hardware Accessories

| Model No.    | Description                                  |

|--------------|----------------------------------------------|

| HP 82411A    | 40K RAM Card                                 |

| HP 82412A    | 32K-128K ROM/EPROM Card                      |

| HP 82430A    | Rechargeable NiCd Battery Pack               |

| HP 82431A    | U.S./Canada Recharger                        |

| HP 82431AB * | Europe Recharger                             |

| HP 82431AG * | Australia Recharger                          |

| HP 82431AU * | U.K. Recharger                               |

| HP 82470A    | RS-232-C Level Converter                     |

| HP 82433A    | HP-94 to Modem Cable                         |

| HP 82434A    | HP-94 to Printer Cable                       |

| HP 82435A    | HP-94 to Level Converter Cable               |

| HP 82436A    | HP-94 to Vectra Cable                        |

| HP 24542G    | Vectra or IBM PC/AT to Level Converter Cable |

| HP 17255D    | IBM PC or PC/XT to Level Converter Cable     |

| HP 39961D    | Smart Wand - Low Resolution                  |

| HP 39963D    | Smart Wand - General Purpose                 |

| HP 39965D    | Smart Wand - High Resolution                 |

<sup>\*</sup> The foreign versions of the recharger (Europe, Australia, and U.K.) are not available at the time this document was printed.

# **40K RAM Card Specifications**

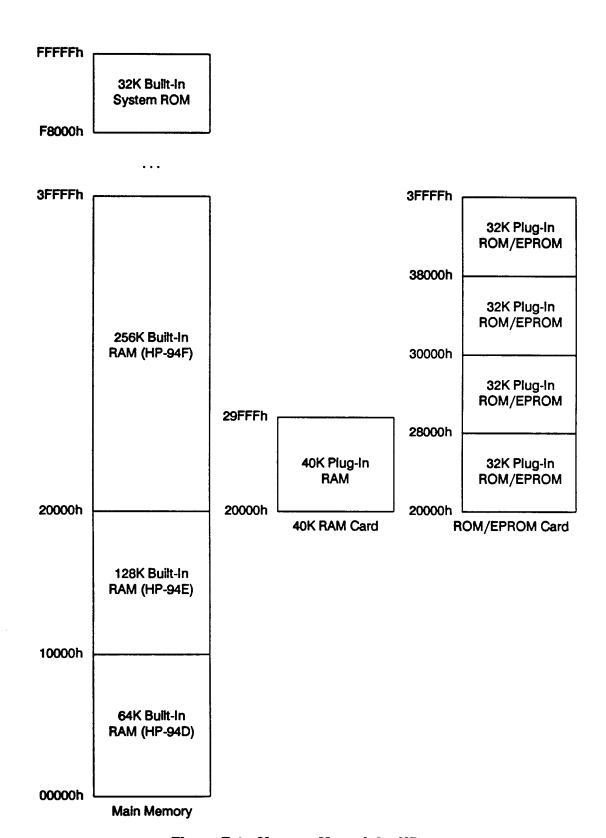

Pin assignments for the HP 82411A 40K RAM Card are described in the "Mechanical Specifications" chapter. The RAM card uses the same Toshiba RAM (TC5565FL-15L) as is used in the HP-94. A CR-2032 (or equivalent) lithium battery is required to provide battery backup for the RAM card.

# **ROM/EPROM Card Specifications**

Pin assignments for the HP 82412A ROM/EPROM Card are described in the "Mechanical Specifications" chapter.

The ROM/EPROM Card has sockets for up to three 32 Kbyte (256 Kbit) ROMs or EPROMs, or up to two 64 Kbyte (512 Kbit) ROMs or EPROMs or their equivalents. There is a socketed jumper on the card that allows selection of the different sizes. The generic names for these ICs are 27C256 for the 32 Kbyte and 27C512 for the 64 Kbyte ICs. The CMOS version of the ROMs or EPROMs must be used. The NMOS versions require more current than is guaranteed by the HP-94. The EPROMs cannot be programmed while in the ROM/EPROM card, but must be programmed in an external EPROM programmer.

A list of the required specifications is provided below to assist in selecting the appropriate parts.

Table 4-2. ROM and EPROM Specifications

| Parameter                    | Min | Max | Units | Comments               |

|------------------------------|-----|-----|-------|------------------------|

| Operating Voltage            | 4.5 | 5.5 | Vdc   | 6.0 V is recommended * |

| <b>Operating Temperature</b> | -10 | +65 | °C    | +14 to 149 °F          |

| Access Time                  |     | 250 | ns    | All parts ≤ 250 ns     |

The manufacturers that make correct size ROMs and EPROMs for use with the ROM/EPROM card and their part designations as of this printing are listed below. You should verify operating voltage, temperature, and speed with the manufacturer before making a final selection.

Table 4-3. ROM and EPROM Manufacturers

| Manufacturer           | 321       | ( IC        | 64K IC    |           |  |

|------------------------|-----------|-------------|-----------|-----------|--|

| manulacturer           | EPROM     | ROM         | EPROM     | ROM       |  |

| Advanced Micro Devices | Am27C256  |             | Am27C512  | -         |  |

| Fujitsu                | MBM27C256 | MB83256     | MBM27C512 | MB83512   |  |

| Hitachi                | HN27C256  | HN613256P   |           |           |  |

| Intel                  | 27C256    | _           | 27C512    |           |  |

| Motorola               | MCM67256  |             | MCM67512  |           |  |

| National Semiconductor | NMC27C256 | <del></del> | NMC27C512 | _         |  |

| NEC                    | μPD27C256 | μPD23C256E  | μPD27C512 | μPD23C512 |  |

| Texas Instruments      | TMS27C256 | TMS47C256   | TMS27C512 | TMS47C512 |  |

| Toshiba                | TC57256   | TMM53257P   | _         | _         |  |

# **Battery Pack Specifications**

The HP-94 uses the HP 82430A Rechargeable Battery Pack. When fully charged, the battery pack has approximately 900 milliamp-hours (mAh) of usable charge. The battery pack is charged whenever an HP 82431 recharger (HP 82431A/AB/AG/AU) is connected to the HP-94. Charging times and currents when charged using one of the HP 82431 rechargers are shown below.

Table 4-4. HP 82430A Rechargeable Battery Pack Specifications

| Parameter        | Symbol          | Min | Typical | Max   | Units | Comments                    |

|------------------|-----------------|-----|---------|-------|-------|-----------------------------|

| Capacity         |                 |     | 900     |       | mAh   |                             |

| Charging Time    | T <sub>ch</sub> | 6   | 10      | 14    | hr    | *                           |

| Charging Current | I <sub>ch</sub> |     | 150 †   |       | mA    | Pack attached<br>to HP-94   |

| Charging Current | l <sub>ch</sub> |     |         | 200 ‡ | mA    | Pack detached<br>from HP-94 |

<sup>\*</sup> The battery pack charging time is independent of HP-94 operating mode. Sufficient current is provided to operate the HP-94 and its principal accessories as well as fully charge the battery pack.

Charging times in excess of 18 hours are not recommended. Extended charging time may reduce the life of the battery pack. It is recommended that periodic "deep discharge - full recharge" cycles be performed to insure that maximum life and charge retention performance of the battery pack is maintained.

The battery pack contains four 2/3 C NiCd batteries completely enclosed in a detachable battery housing. All NiCd batteries are capable of extremely high short circuit currents. A thermal protector is built into the battery pack to prevent a constant short circuit condition. Since this circuit is temperature-sensitive, ambient conditions at or above its 75 °C temperature rating will cause a temporary open circuit in the battery pack. The HP-94 will then behave as if no battery pack is connected. When the short circuit or high temperature condition is removed, the battery pack short circuit protector will again close and the battery pack will continue normal operation.

WARNING Never connect multiple battery packs in parallel while charging. Each individual pack should be blocked with a diode to prevent short circuit current from a failed cell from flowing into good cells of other packs.

The battery pack connector specifications are described in the "Mechanical Specifications" chapter.

<sup>†</sup> The battery is connected to the recharger through a 2.7 Ω current-limiting resistor in series with a Schottky blocking diode. The actual charging current will vary as the battery pack voltage increases from the discharged state to the full charged state.

<sup>‡</sup> Charging at currents greater than 200 mA for extended periods of time may damage the battery pack.

## **Guidelines for Using Rechargeable Batteries**

The following is usage information and cautions about using rechargeable batteries.

### CAUTION

To avoid damage to the handheld computer, use only the batteries and recharger designated by Hewlett-Packard for the computer. Also, do not allow the batteries to discharge beyond their available capacity — recharge as soon as possible after the low battery indication appears. Allowing rechargeable batteries to discharge beyond their maximum limit can damage the batteries.

- Recharging batteries before they are low may eventually decrease their charging capacity.

- Do not overcharge the batteries by allowing them to recharge for longer than the recommended time. Shorter charging times will reduce the operating time before recharging is required, but will not harm the batteries.

- Do not leave the recharger permanently connected to the machine. Doing so decreases the useful life of the batteries.

- Do not use the recharger if it appears to have loose contacts, a cracked housing, or a damaged cord.

- Properly dispose of the batteries when they no longer adequately hold a charge or when they appear damaged.

WARNING To prevent injury, keep all batteries out of the reach of children and properly dispose of exhausted batteries. Do not mutilate or puncture batteries, and do not dispose of them in fire. Exposure to excessive heat can cause release of toxic fumes or explosion.

# **Recharger Specifications**

The HP 82431 Recharger (HP 82431A/AB/AG/AU) supplies charging current to the HP-94's NiCd battery pack. The recharger is designed to supply sufficient current to charge the batteries even while the HP-94 is operating.

Table 4-5. HP 82431 Recharger Specifications

| Parameter       | Symbol           | Min  | Typical | Max        | Units | Comments         |

|-----------------|------------------|------|---------|------------|-------|------------------|

| Input Voltage   | V <sub>ac</sub>  | 108  | 120     | 132        | Vac   | HP 82431A        |

|                 | <u> </u>         | 198  | 220     | 242        | Vac   | HP 82431AB       |

|                 |                  | 216  | 240     | 264        | Vac   | HP 82431AG/AU    |

| Input Current   | lac              |      |         | 80         | mA    | HP 82431A        |

| pur ourror      |                  |      |         | 40         | mA    | HP 82431AB/AG/AU |

| Input Frequency | Ifr              | 57.5 | 60      | 62.5       | Hz    | HP 82431A        |

|                 | "                | 47.5 | 50      | <b>5</b> 5 | Hz    | HP 82431AB/AG/AU |

| Output Voltage  | V <sub>rch</sub> | 6.2  |         | 6.7        | Vdc   |                  |

| Output Current  | I <sub>rch</sub> | 1    |         | 400        | mA    | *                |

Refer to "Battery Pack Specifications" for details about the charging current actually supplied to the pattery pack

# **Level Converter Specifications**

The HP-94 serial port outputs CMOS logic levels (refer to "Electrical Specifications"). Some RS-232 devices require that proper RS-232 voltage levels be provided for their serial interfaces to operate properly. These devices require the use of the HP 82470A RS-232-C Level Converter.

The level converter modifies the 0 to  $V_{cc}$  voltage level outputs from the HP-94 serial port to  $\pm 9$  V EIA RS-232-C voltage levels. Additionally, the level converter's 25-pin connector inputs and outputs meet all RS-232 timing and load specifications. RS-232 voltage level inputs to the level converter's 25-pin connector are internally shifted to the 0 to  $V_{cc}$  range the HP-94 expects, and then are output to the HP-94 using the 15-pin connector.

When the serial port is disabled, the control lines are turned off (set to 0 volts). This is different than most AC-powered serial devices, in which the control lines are high (-3 volts or less) because the serial port is powered whenever the device is on.

Connection is made between the HP-94 and the level converter using an HP 82435A 1/4 meter cable. The level converter is powered by the HP-94 using pin 9 of the serial port ( $V_{rs}$ ). The output voltage  $V_{rs}$  is activated under program control when the serial port is enabled (refer to the "Serial Port" chapter in the operating system section of this manual). Typical power consumption by the level converter is 25 mA when active with a standard RS-232-C load at 9600 baud and  $V_{cc} = 6.0$  volts ( $V_{rs} = V_{cc}$ -0.1 V).

Below are the pin assignments for both the 15- and 25-pin connectors on the level converter.

Table 4-6. HP 82470A RS-232-C Level Converter Pin Assignments

| 25-Pin Fema                 | tor    | 15-Pin Female Connector |         |          |                            |

|-----------------------------|--------|-------------------------|---------|----------|----------------------------|

| Signal Name                 | Symbol | Pin No.                 | Pin No. | Symbol   | HP-94 Signal Name          |

| Frame Ground                | FG     | Housing                 | Housing | FG       | Frame Ground               |

| Transmitted Data            | TxD    | 2                       | 2       | TxD      | Transmitted Data           |

| Received Data               | RxD    | 3                       | 3       | RxD      | Received Data              |

| Request To Send             | RTS    | 4                       | 4       | RTS      | Request To Send            |

| Clear To Send               | CTS    | 5                       | 5       | CTS      | Clear To Send              |

| Data Set Ready              | DSR    | 6                       | 6       | DSR      | Data Set Ready             |

| Signal Ground               | SG     | 7                       | 7       | SG       | Signal Ground              |

| Data Carrier Detect         | DCD    | 8                       | 8       | DCD      | Data Carrier Detect        |

| Not Connected               | NC     | 9                       | 9       | $V_{rs}$ | Switched V <sub>cc</sub> * |

| Data Terminal Ready         | DTR    | 20                      | 15      | DTR      | Data Terminal Ready        |

| * HP 82470A level converted | nower  |                         |         |          |                            |

## When to Use the Level Converter

RS-232-C specifications require that input signal levels at the input of a device be greater than +3 or less than -3 volts. RS-232 output voltages experience a greater voltage swing to prevent signal degradation and line noise from interfering with communication signals. However, many available line receivers do not actually require voltage swings of these levels. The HP-94 system can take advantage of this by not requiring that the level converter be used when communicating with these devices.

The HP-94 will switch its RS-232 outputs between CMOS logic levels, where  $V_{cc}$  will be between 4.5 and 6.0 volts. This provides logic low levels of less than 0.2 volts and logic high levels of greater than  $V_{cc}$ -0.2 volts. Thus, any line receiver that will respond with high-to-low and low-to-high transitions in this range of logic 0/1 values will not need to have true RS-232 levels at its inputs to properly detect the logic level.

The line receivers that can communicate directly with the HP-94 (that is, no level converter required) are listed below. Certain parts listed must be operated in the specified mode or configuration, so special attention must be paid to the comments.

Table 4-7. Line Receivers That Do Not Require Level Converter

| Part Number | Manufacturer                         | Comments                                  |

|-------------|--------------------------------------|-------------------------------------------|

| 1489        | National Semiconductor<br>Motorola * | Response (threshold) control must be open |

| 75189       | Texas Instruments                    | Response (threshold) control must be open |

| 75154       | Texas Instruments                    | Response (threshold) control must be open |

| MAX232      | Maxim                                | , , ,                                     |

| MC145406    | Motorola                             |                                           |

| 74HC14      | many manufacturers                   |                                           |

### CAUTION

When using the HP-94 system without a level converter, special care must be taken to ensure that the interconnection cables are sufficiently short to prevent signal degradation. It is recommended that all communications cable for use with the HP-94 that do not use the level converter be less than 3 meters in length.

### **Cables**

There are several cables available to allow configuration of the HP-94 in a system. The connections for each of these cables are provided in the tables that follow in this section. Cable lengths are 1 meter unless specified otherwise.

### **Modem Cable**

The HP 82433A cable is used to connect the HP-94 to modems that do not require a level converter. It is specifically designed for use with Hayes Smartmodems, but is usable with many other modems as well.

Table 4-8. HP-94 to Modem Cable

| HP<br>15-Pin Male      | Modem<br>25-Pin Male Connector |           |         |        |            |

|------------------------|--------------------------------|-----------|---------|--------|------------|

| Signal Name            | Signal Name Symbol Pin No.     |           |         | Symbol | Direction  |

| Frame Ground           | FG                             | Housing   | Housing | AA     | N/A        |

| Transmitted Data       | TxD                            | 2         | 2       | BA     | To Modem   |

| Received Data          | RxD                            | 3         | 3       | BB     | From Modem |

| Request To Send        | RTS                            | 4         | 4       | CA *   | To Modem   |

| Clear To Send          | CTS                            | 5         | 5       | CB     | From Modem |

| Data Set Ready         | DSR                            | 6         | 6       | CC     | From Modem |

| Signal Ground          | SG                             | 7         | 7       | AB     | N/A        |

| Data Carrier Detect    | DCD                            | 8         | 8       | CF     | From Modem |

| Data Terminal Ready    | DTR                            | 15        | 20      | CD     | To Modem   |

| * Hayes Smartmodems do | not implement ti               | nis line. |         |        |            |

The HP-94 has receive all the necessary approvals for connecting to modems in the U.S. Some countries require that the product and its interface cable be approved prior to connecting to a modem. Contact your local Hewlett-Packard sales office to verify that the HP-94 is approved for your specific location.

### **Printer Cable**

The HP 82434A cable is used to connect the HP-94 to RS-232-C printers that do not require a level converter. It is specifically designed for use with Hewlett-Packard ThinkJet printers (HP 2225D), but is usable with many other printers as well.

Table 4-9. HP-94 to Printer Cable

| HP-94<br>15-Pin Male Connector |                                |                                                                                      | Printer<br>25-Pin Male Connector |        |                     |  |  |  |  |

|--------------------------------|--------------------------------|--------------------------------------------------------------------------------------|----------------------------------|--------|---------------------|--|--|--|--|

| Signal Name                    | Signal Name   Symbol   Pin No. |                                                                                      |                                  | Symbol | Signal Name         |  |  |  |  |

| Frame Ground                   | FG                             | Housing                                                                              | Housing                          | AA     | Protective Ground   |  |  |  |  |

| Transmitted Data               | TxD                            | 2                                                                                    | 3                                | ₿B     | Received Data       |  |  |  |  |

| Received Data                  | RxD                            | 3                                                                                    | 2                                | ВА     | Transmitted Data    |  |  |  |  |

| Request To Send                | RTS                            | 4                                                                                    | 5                                | CB *   | Clear To Send       |  |  |  |  |

| Clear To Send                  | CTS                            | 5                                                                                    | 4                                | CA     | Request To Send     |  |  |  |  |

| Data Set Ready                 | DSR                            | 6                                                                                    | 20                               | CD     | Data Terminal Ready |  |  |  |  |

| Signal Ground                  | SG                             | 7                                                                                    | 7                                | AB     | Signal Ground       |  |  |  |  |

| * Many printers (including     | ng the Hewlett-F               | * Many printers (including the Hewlett-Packard ThinkJet) do not implement this line. |                                  |        |                     |  |  |  |  |

## **Level Converter Cable**

When using the level converter, an HP 82435A 1/4-meter cable is required. This cable provides a straight-through connection between the HP-94 and the level converter.

Table 4-10. HP-94 to Level Converter Cable

| HP-94<br>15-Pin Male Connector |                   |         | Level Converter<br>15-Pin Female Connector |                   |                          |

|--------------------------------|-------------------|---------|--------------------------------------------|-------------------|--------------------------|

| Signal Name                    | Symbol            | Pin No. | Pin No.                                    | Symbol            | Signal Name              |

| Frame Ground                   | FG                | Housing | Housing                                    | FG                | Frame Ground             |

| Transmitted Data               | TxD               | 2       | 2                                          | TxD               | Transmitted Data         |

| Received Data                  | RxD               | 3       | 3                                          | RxD               | Received Data            |

| Request To Send                | RTS               | 4       | 4                                          | RTS               | Request To Send          |

| Clear To Send                  | CTS               | 5       | 5                                          | CTS               | Clear To Send            |

| Data Set Ready                 | DSR               | 6       | 6                                          | DSR               | Data Set Ready           |

| Signal Ground                  | SG                | 7       | 7                                          | SG                | Signal Ground            |

| Data Carrier Detect            | DCD               | 8       | 8                                          | DCD               | Data Carrier Detect      |

| Switched V <sub>cc</sub>       | V <sub>rs</sub> * | 9       | 9                                          | V <sub>rs</sub> * | Switched V <sub>cc</sub> |

| Data Terminal Ready            | DTR               | 15      | 15                                         | DTR               | Data Terminal Ready      |

| * HP 82470A level converted    | power.            | •       |                                            |                   | <u> </u>                 |

## **Vectra Cable**

The HP 82436A 2-meter cable is used whenever direct communication between the HP-94 and a 9-pin serial port on an HP Vectra personal computer. Each of the two Vectra serial interfaces has one 9-pin port: the HP 24540A Serial/Parallel Interface, and the HP 24541A Dual Serial Interface. HP supplies no cables that connect the HP-94 directly to the 25-pin port on the Vectra Dual Serial Interface.

Table 4-11. HP-94 to Vectra Cable

| Vectra 9-Pin Female Connector  |      |         | HP-94<br>15-Pin Male Connector |        |                     |

|--------------------------------|------|---------|--------------------------------|--------|---------------------|

| Signal Name   Symbol   Pin No. |      |         | Pin No.                        | Symbol | Signal Name         |

| Protective Ground              | AA   | Housing | Housing                        | FG     | Frame Ground        |

| Received Data                  | BB   | 2       | 2                              | TxD    | Transmitted Data    |

| Transmitted Data               | BA   | 3       | 3                              | RxD    | Received Data       |

| Data Terminal Ready            | CD   | 4       | 5 *                            | CTS    | Clear to Send       |

| Data Terminal Ready            | CD   | 4       | 6*                             | DSR    | Data Set Ready      |

| Signal Ground                  | AB   | 5       | 7                              | SG     | Signal Ground       |

| Data Set Ready                 | l cc | 6*      | 15                             | DTR    | Data Terminal Ready |

| Clear to Send                  | СВ   | 8*      | 15                             | DTR    | Data Terminal Ready |

<sup>\*</sup> Pins 6 and 8 are tied together on the 9-pin connector, and pins 5 and 6 are tied together on the 15-pin connector.

# Vectra or IBM PC/AT to Level Converter Cable

The HP-94 can communicate directly with the HP Vectra computer through the HP 82436A cable, without using a level converter. For applications that require extended cable lengths or desire the level converter option, the HP 24542G Serial Printer/Plotter Cable can be used. When communicating with the IBM PC/AT, a level converter is required, and this cable must be used. The level converter is then connected to the HP-94 using the HP 82435A cable.

Table 4-12. Vectra or IBM PC/AT to Level Converter Cable

| Vectra or IBM PC/AT<br>9-Pin Female Connector |        |         | Level Converter<br>25-Pin Male Connector |        |                     |

|-----------------------------------------------|--------|---------|------------------------------------------|--------|---------------------|

| Signal Name                                   | Symbol | Pin No. | Pin No.                                  | Symbol | Signal Name         |

| Protective Ground                             | AA     | Housing | Housing                                  | FG     | Frame Ground        |

| Data Carrier Detect                           | CF     | 1       | 4                                        | RTS    | Request To Send     |

| Received Data                                 | BB     | 2       | 2                                        | TxD    | Transmitted Data    |

| Transmitted Data                              | BA     | 3       | 3                                        | RxD    | Received Data       |

| Data Terminal Ready                           | CD     | 4       | 5 *                                      | CTS    | Clear To Send       |

| Data Terminal Ready                           | CD     | 4       | 6*                                       | DSR    | Data Set Ready      |

| Signal Ground                                 | AB     | 5       | 7                                        | SG     | Signal Ground       |

| Data Set Ready                                | cc     | 6*      | 20                                       | DTR    | Data Terminal Ready |

| Request To Send                               | CA     | 7       | 8                                        | DCD    | Data Carrier Detect |

| Clear To Send                                 | СВ     | 8*      | 20                                       | DTR    | Data Terminal Ready |

<sup>\*</sup> Pins 6 and 8 are tied together on the 9-pin connector, and pins 5 and 6 are tied together on the 25-pin connector.

## IBM PC or PC/XT to Level Converter Cable

When using an IBM PC or PC/XT to communicate with the HP-94, a level converter is required. The HP 17255D cable connects the 25-pin IBM serial port connector to the 25-pin connector on the level converter. The level converter is then connected to the HP-94 using the HP 82435A cable.

Table 4-13. IBM PC or PC/XT to Level Converter Cable

| IBM PC or PC/XT 25-Pin Female Connector |     |           | Level Converter<br>25-Pin Male Connector |        |                     |

|-----------------------------------------|-----|-----------|------------------------------------------|--------|---------------------|

| Signal Name Symbol Pin No.              |     |           | Pin No.                                  | Symbol | Signal Name         |

| Frame Ground                            | FG  | Housing * | Housing *                                | FG     | Frame Ground        |

| Transmitted Data                        | TxD | 2         | 3                                        | RxD    | Received Data       |

| Received Data                           | RxD | 3         | 2                                        | TxD    | Transmitted Data    |

| Clear To Send                           | CTS | 5†        | 20                                       | DTR    | Data Terminal Ready |

| Data Set Ready                          | DSR | 6†        | 20                                       | DTR    | Data Terminal Ready |

| Signal Ground                           | SG  | 7         | 7                                        | SG     | Signal Ground       |

| Data Terminal Ready                     | DTR | 20        | 5†                                       | CTS    | Clear To Send       |

| Data Terminal Ready                     | DTR | 20        | 6†                                       | DSR    | Data Set Ready      |

<sup>\*</sup> Pin 1 is connected to frame ground (housing) on both connectors.

### **Bar Code Readers**

The primary bar code readers for the HP-94 are the three HP Smart Wands: HP 39961D (low resolution), HP 39963D (general purpose), and HP 39965D (high resolution). Contact your sales office for complete literature and specifications for these wands.

# Connecting the Serial Port to a Smart Wand

HP Smart Wands can be configured in one of two ways:

- By scanning bar code configuration menus (optical configuration)

- By sending configuration escape sequences to the Smart Wand

When a Smart Wand is connected to the bar code port, only the first approach is available because the bar code port is read-only. The second approach is available if the Smart Wand can be connected to the serial port. To support this use, Hewlett-Packard supplies a low-level bar code handler with the HP-94 Software Development System called HNSP that allows "smart" bar code scanning devices to be connected to the serial port.

HP Smart Wands are supplied with a 5-pin, 240° circular DIN connector, but at this printing are not available with a 15-pin D-type connector that would connect to the serial port. Below are the connections for a cable that will connect the serial port to a Smart Wand. This cable is not available from Hewlett-Packard — the connections are provided to allow a developer to make the cable.

<sup>†</sup> Pins 5 and 6 are tied together on both connectors.

Table 4-14. HP-94 Serial Port to Smart Wand Cable

| HP-94<br>15-Pin Male Connector |                   |           | Smart Wand<br>5-Pin or 6-Pin Female Connector |                   |                          |

|--------------------------------|-------------------|-----------|-----------------------------------------------|-------------------|--------------------------|

| Signal Name                    | Symbol            | Pin No.   | Pin No.                                       | Symbol            | Signal Name              |

| Frame Ground                   | FG                | Housing * | Housing *                                     | FG                | Frame Ground             |

| Transmitted Data               | TxD               | 2         | 4                                             | RxD               | Received Data            |

| Received Data                  | RXD               | 3         | 2                                             | TxD               | Transmitted Data         |

| Request To Send                | RTS               | 4+        | _                                             | NC                | Not Connected            |

|                                | CTS               | 5†        | <u> </u>                                      | NC                | Not Connected            |

| Clear To Send                  |                   | 7         | 3                                             | SG                | Signal Ground            |

| Signal Ground                  | SG                | 1 '       | 3                                             |                   | Switched V <sub>cc</sub> |

| Switched V <sub>cc</sub>       | V <sub>rs</sub> ‡ | 9         |                                               | V <sub>rs</sub> ‡ | SWITCHEG VCC             |

<sup>\*</sup> The shield or braid must be connected to frame ground (housing).

<sup>†</sup> Pins 4 and 5 are tied together on the 15-pin connector.

<sup>‡</sup> HP Smart Wand power.

# **Data Sheets**

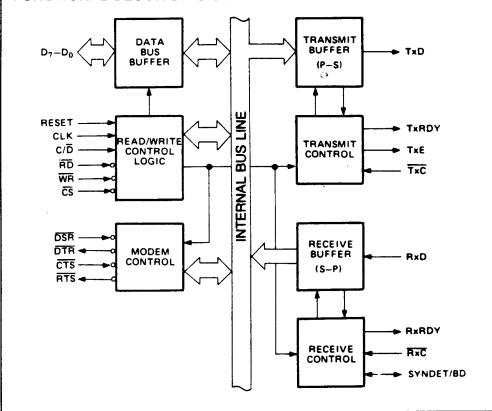

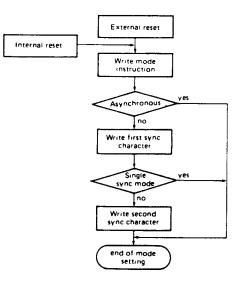

# **Data Sheets**

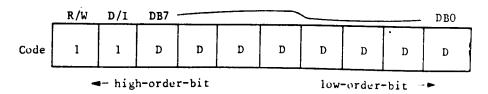

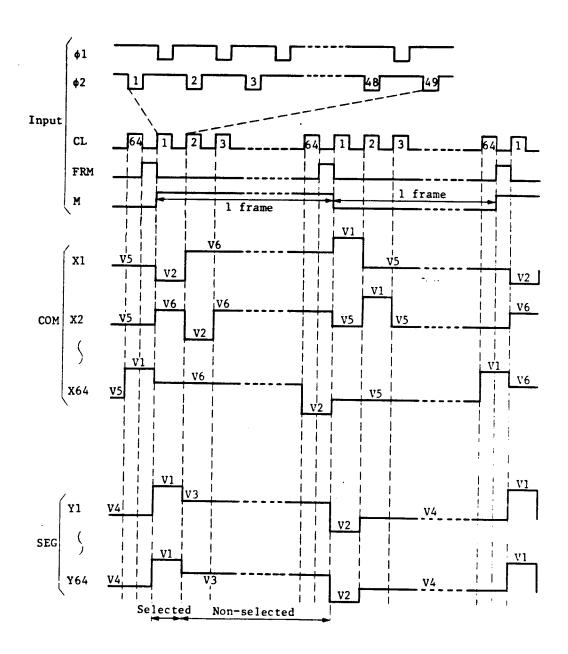

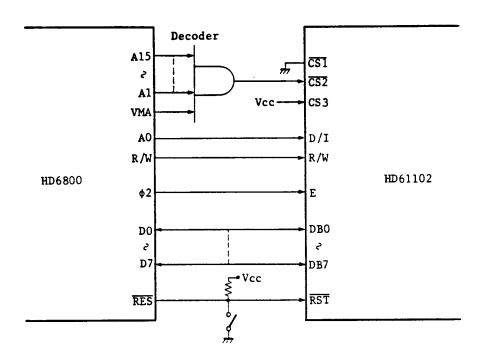

This chapter contains copies of manufacturer's data sheets for the following four ICs:

- NEC µPD70108 (V20) Microprocessor

- OKI MSM82C51A Universal Asynchronous Receiver Transmitter (UART)

- Hitachi HD61102A LCD Column Driver

- Epson RTC-58321 Real-Time Clock

These data sheets provide reference information for developers whose application interacts directly with the IC, independent of the HP-94 operating system. Refer to the appropriate chapters in the "Operating System" for information about how these ICs are used in the HP-94, what I/O control registers are associated with each IC, and what built-in software is available already to control them.

Ç

NEC  $\mu$ PD70108 (V20) Microprocessor Data Sheet

# μPD70108 (V20) HIGH-PERFORMANCE 16-BIT MICROPROCESSOR

Revision 3

November 1985

## **Description**

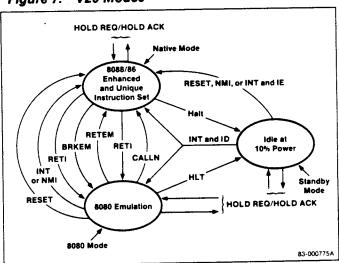

The  $\mu$ PD70108 (V20) is a CMOS 16-bit microprocessor with internal 16-bit architecture and an 8-bit external data bus. The  $\mu$ PD70108 instruction set is a superset of the  $\mu$ PD8086/8088; however, mnemonics and execution times are different. The  $\mu$ PD70108 additionally has a powerful instruction set including bit processing, packed BCD operations, and high-speed multiplication/division operations. The  $\mu$ PD70108 can also execute the entire 8080 instruction set and comes with a standby mode that significantly reduces power consumption. It is software-compatible with the  $\mu$ PD70116 16-bit microprocessor.

## **Features**

|   | Minimum instruction execution time: 250 ns     |

|---|------------------------------------------------|

|   | (at 8 MHz)                                     |

|   | Maximum addressable memory: 1 Mbyte            |

|   | Abundant memory addressing modes               |

|   | 14 x 16-bit register set                       |

|   | 101 instructions                               |

|   | Instruction set is a superset of µPD8086/8088  |

| ì | instruction set                                |

| ' | Bit, byte, word, and block operations          |

|   | Bit field operation instructions               |

|   | <br>Packed BCD instructions                    |

|   | Multiplication/division instruction execution  |

|   | time: 4 $\mu$ s to 6 $\mu$ s (at 8 MHz)        |

|   | High-speed block transfer instructions:        |

|   | 1 Mbyte/s (at 8 MHz)                           |

|   | High-speed calculation of effective addresses: |

|   | 2 clock cycles in any addressing mode          |

|   | Maskable (INT) and nonmaskable (NMI)           |

|   | interrupt inputs                               |

|   | IEEE-796 bus compatible interface              |

|   | 8080 emulation mode                            |

|   | CMOS technology                                |

|   | Low-power consumption                          |

|   | Low-power standby mode                         |

|   | Single power supply                            |

|   | 5 MHz 8 MHz or 10 MHz clock                    |

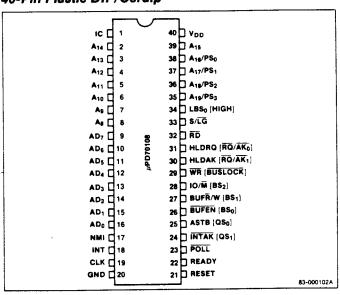

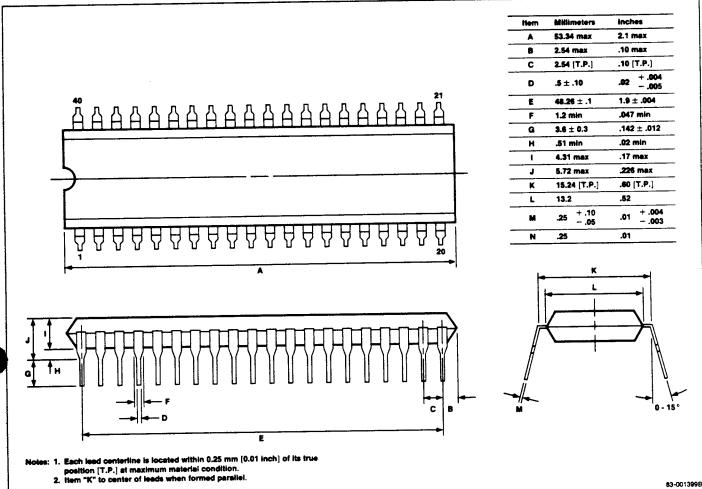

# **Ordering Information**

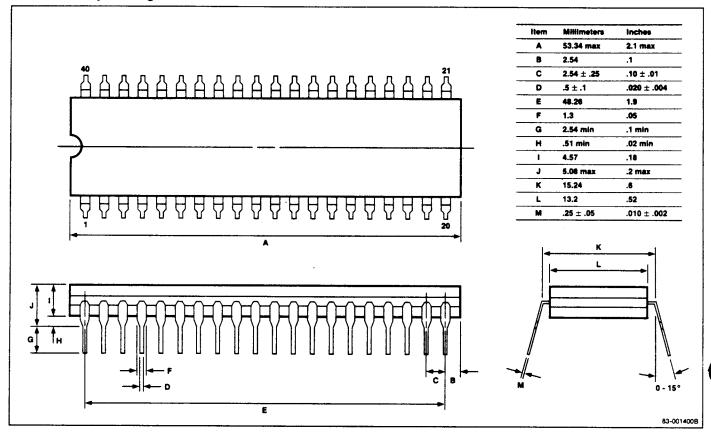

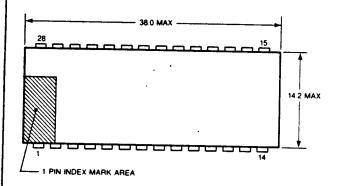

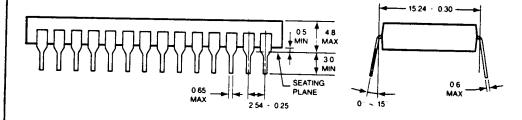

| Part<br>Number | Package Type       | Max Frequency of Operation |

|----------------|--------------------|----------------------------|

| μPD70108C-5    | 40-pin plastic DIP | 5 MHz                      |

| μPD70108C-8    | 40-pin plastic DIP | 8 MHz                      |

| μPD70108D-5    | 40-pin ceramic DIP | 5 MHz                      |

| μPD70108D-8    | 40-pin ceramic DIP | 8 MHz                      |

| μPD70108D-10   | 40-pin ceramic DIP | 10 MHz                     |

| μPD70108G-5    | 52-pin flat pack   | 5 MHz                      |

| μPD70108G-8    | 52-pin flat pack   | 8 MHz                      |

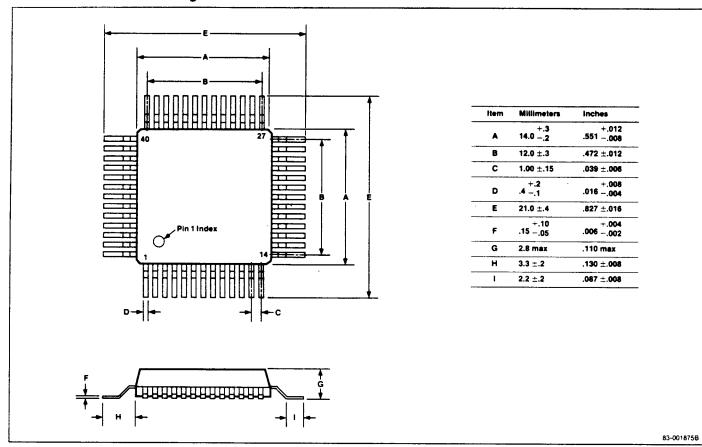

| μPD70108L-5    | 44-pin PLCC        | 5 MHz                      |

| μPD70108L-8    | 44-pin PLCC        | 8 MHz                      |

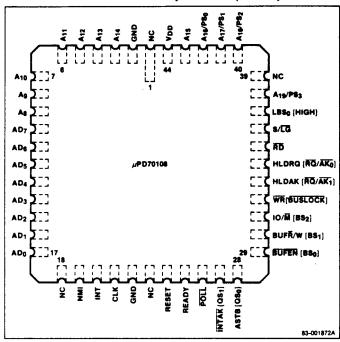

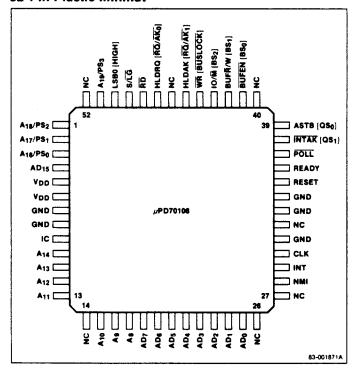

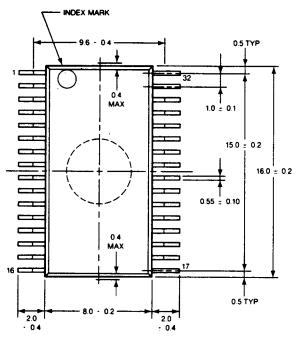

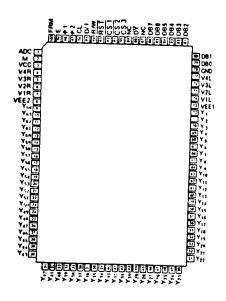

# **Pin Configurations**

# 40-Pin Plastic DIP/Cerdip

## Pin Configurations (cont)

### 44-Pin Plastic Leadless Chip Carrier (PLCC)

### 52-Pin Plastic Miniflat

## Pin Identification

| No.     | Symbol                                                                 | Direction       | Function                                                                    |

|---------|------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------|

| 1       | IC*                                                                    |                 | Internally connected                                                        |

| 2 - 8   | A <sub>14</sub> - A <sub>8</sub>                                       | Out             | Address bus, middle bits                                                    |

| 9 - 16  | AD <sub>7</sub> - AD <sub>0</sub>                                      | In/Out          | Address/data bus                                                            |

| 17      | NMI                                                                    | In              | Nonmaskable interrupt input                                                 |

| 18      | INT                                                                    | In              | Maskable interrupt input                                                    |

| 19      | CLK                                                                    | ln              | Clock input                                                                 |

| 20      | GND                                                                    |                 | Ground potential                                                            |

| 21      | RESET                                                                  | In              | Reset input                                                                 |

| 22      | READY                                                                  | In              | Ready input                                                                 |

| 23      | POLL                                                                   | In              | Poll input                                                                  |

| 24      | INTAK (QS <sub>1</sub> )                                               | Out             | interrupt acknowledge<br>output (queue status bit<br>1 output)              |

| 25      | ASTB (QS <sub>0</sub> )                                                | Out             | Address strobe output (queue status bit 0 output)                           |

| 26      | BUFEN (BS <sub>0</sub> )                                               | Out             | Buffer enable output<br>(bus status bit 0 output)                           |

| 27      | BUFŘ/W (BS <sub>1</sub> )                                              | Out             | Buffer read/write output (bus status bit 1 output)                          |

| 28      | 10/ <b>M</b> (BS <sub>2</sub> )                                        | Out             | Access is 1/0 or memory (bus status bit 2 output)                           |

| 29      | WR (BUSLOCK)                                                           | Out             | Write strobe output (bus lock output)                                       |

| 30      | HLDAK (RQ/AK <sub>1</sub> )                                            | Out<br>(In/Out) | Holdacknowledgeoutput,<br>(bus hold request input/<br>acknowledge output 1) |

| 31      | HLDRQ (RQ/AK <sub>0</sub> )                                            | In<br>(In/Out)  | Hold request input (bus<br>hold request input/<br>acknowledge output 0)     |

| 32      | RD                                                                     | Out             | Read strobe output                                                          |

| 33      | S/ <del>LG</del>                                                       | In              | Small-scale/large-scale system input                                        |

| 34      | LBS <sub>0</sub> (HIGH)                                                | Out             | Latched bus status output<br>0 (always high in<br>large-scale systems)      |

| 35 - 38 | A <sub>19</sub> /PS <sub>3</sub> -<br>A <sub>16</sub> /PS <sub>0</sub> | Out             | Address bus, high bits or processor status output                           |

| 39      | A <sub>15</sub>                                                        | Out             | Address bus, bit 15                                                         |

| 40      | V <sub>DD</sub>                                                        |                 | Power supply                                                                |

Notes: \* IC should be connected to ground.

Where pins have different functions in small- and largescale systems, the large-scale system pin symbol and function are in parentheses.

Unused input pins should be tied to ground or  $V_{DD}$  to minimize power dissipation and prevent the flow of potentially harmful currents.

## Pin Functions

Some pins of the  $\mu$ PD70108 have different functions according to whether the microprocessor is used in a small- or large-scale system. Other pins function the same way in either type of system.

## A<sub>15</sub> - A<sub>8</sub> [Address Bus]

For small- and large-scale systems.

The CPU uses these pins to output the middle 8 bits of the 20-bit address data. They are three-state outputs and become high impedance during hold acknowledge.

## AD7 - AD0 [Address/Data Bus]

For small- and large-scale systems.

The CPU uses these pins as the time-multiplexed address and data bus. When high, an AD bit is a one; when low, an AD bit is a zero. This bus contains the lower 8 bits of the 20-bit address during T1 of the bus cycle and is used as an 8-bit data bus during T2, T3, and T4 of the bus cycle.

Sixteen-bit data I/O is performed in two steps. The low byte is sent first, followed by the high byte. The address/data bus is a three-state bus and can be at a high or low level during standby mode. The bus will be high impedance during hold and interrupt acknowledge.

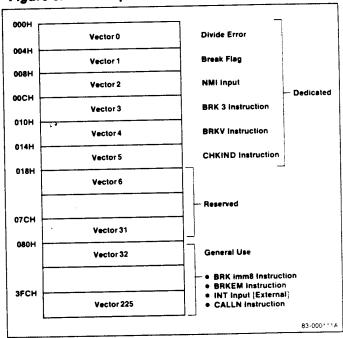

## NMI [Nonmaskable Interrupt]

For small- and large-scale systems.

This pin is used to input nonmaskable interrupt requests. NMI cannot be masked by software. This input is positive edge triggered and must be held high for five clocks to guarantee recognition. Actual interrupt processing begins, however, after completion of the instruction in progress.

The contents of interrupt vector 2 determine the starting address for the interrupt-servicing routine. Note that a hold request will be accepted even during NMI acknowledge.

This interrupt will cause the  $\mu$ PD70108 to exit the standby mode.

## INT [Maskable Interrupt]

For small- and large-scale systems.

This pin is an interrupt request that can be masked by software.

INT is active high level and is sensed during the last clock of the instruction. The interrupt will be accepted if the interrupt enable flag IE is set. The CPU outputs the INTAK signal to inform external devices that the interrupt request has been granted. INT must be asserted until the interrupt acknowledge is returned.

If NMI and INT interrupts occur at the same time, NMI has higher priority than INT and INT cannot be

accepted. A hold request will be accepted during INT acknowledge.

This interrupt causes the  $\mu$ PD70108 to exit the standby mode.

## CLK [Clock]

For small- and large-scale systems.

This pin is used for external clock input.

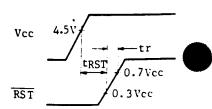

## RESET [Reset]

For small- and large-scale systems.

This pin is used for the CPU reset signal. It is an active high level. Input of this signal has priority over all other operations. After the reset signal input returns to a low level, the CPU begins execution of the program starting at address FFFF0H.

In addition to causing normal CPU start, RESET input will cause the  $\mu$ PD70108 to exit the standby mode.

## READY [Ready]

For small- and large-scale systems.

When the memory or I/O device being accessed cannot complete data read or write within the CPU basic access time, it can generate a CPU wait state (Tw) by setting this signal to inactive (low level) and requesting a read/write cycle delay.

If the READY signal is active (high level) during either the T3 or Tw state, the CPU will not generate a wait state.

## POLL [Poll]

For small- and large-scale systems.

The CPU checks this input upon execution of the POLL instruction. If the input is low, then execution continues. If the input is high, the CPU will check the POLL input every five clock cycles until the input becomes low again.

The POLL and READY functions are used to synchronize CPU program execution with the operation of external devices.

## RD [Read Strobe]

For small- and large-scale systems.

The CPU outputs this strobe signal during data read from an I/O device or memory. The  $IO/\overline{M}$  signal is used to select between I/O and memory.

The three-state output is held high during standby mode and enters the high-impedance state during hold acknowledge.

## S/LG [Small/Large]

For small- and large-scale systems.

This signal determines the operation mode of the CPU. This signal is fixed at either a high or low level. When

this signal is a high level, the CPU will operate in smallscale system mode, and when low, in the large-scale system mode. A small-scale system will have at most one bus master such as a DMA controller device on the bus. A large-scale system can have more than one bus master accessing the bus as well as the CPU.

Pins 24 to 31 and pin 34 function differently depending on the operating mode of the CPU. Separate nomenclature is adopted for these signals in the two operating modes.

|         |                  | Function           |

|---------|------------------|--------------------|

| Pin No. | S/LG-high        | S/LG-low           |

| 24      | INTAK            | QS <sub>1</sub>    |

| 25      | ASTB             | QS <sub>0</sub>    |

| 26      | BUFEN            | BS <sub>0</sub>    |

| 27      | BUFR/W           | BS <sub>1</sub>    |

| 28      | 10/ <b>M</b>     | BS <sub>2</sub>    |

| 29      | <b>₩</b> R       | BUSLOCK            |

| 30      | HLDAK            | RQ/AK <sub>1</sub> |

| 31      | HLDRQ            | RQ/AK <sub>0</sub> |

| 34      | LBS <sub>0</sub> | Always high        |

## **INTAK** [Interrupt Acknowledge]

For small-scale systems.

The CPU generates the INTAK signal low when it accepts an INT signal.

The interrupting device synchronizes with this signal and outputs the interrupt vector to the CPU via the data bus  $(AD_7 - AD_0)$ .

## **ASTB** [Address Strobe]

For small-scale systems.

The CPU outputs this strobe signal to latch address information at an external latch.

ASTB is held at a low level during standby mode and hold acknowledge.

## **BUFEN** [Buffer Enable]

For small-scale systems.

This is used as the output enable signal for an external bidirectional buffer. The CPU generates this signal during data transfer operations with external memory or I/O devices or during input of an interrupt vector.

This three-state output is held high during standby mode and enters the high-impedance state during hold acknowledge.

## **BUFR/W** [Buffer Read/Write]

For small-scale systems.

The output of this signal determines the direction of data transfer with an external bidirectional buffer. A

high output causes transmission from the CPU to the external device; a low signal causes data transfer from the external device to the CPU.

BUFR/W is a three-state output and becomes high impedance during hold acknowledge.

## IO/M [IO/Memory]

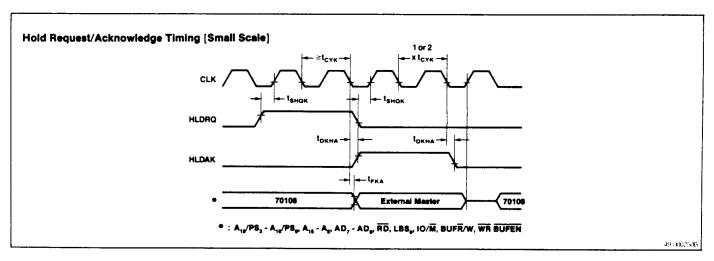

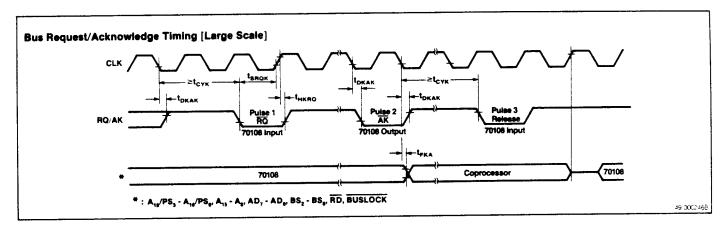

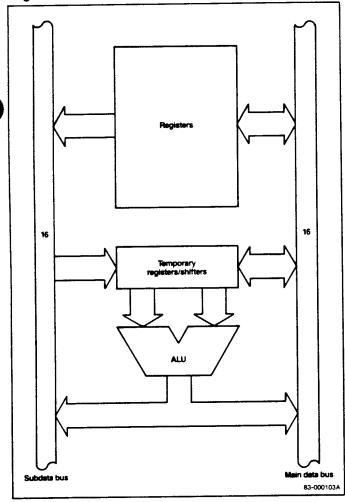

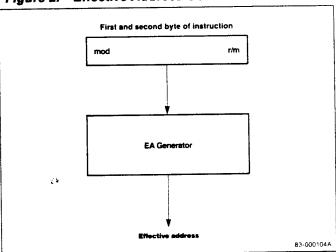

For small-scale systems.